## The Transition to IA-64

#### Ken Kroeker

SeniorTechnicalConsultant

PartnerTechnologyAccessCenter

Hewlett-PackardCompany

120CenturyRoadWest

Paramus,NewJersey

ken\_kroeker@hp.com

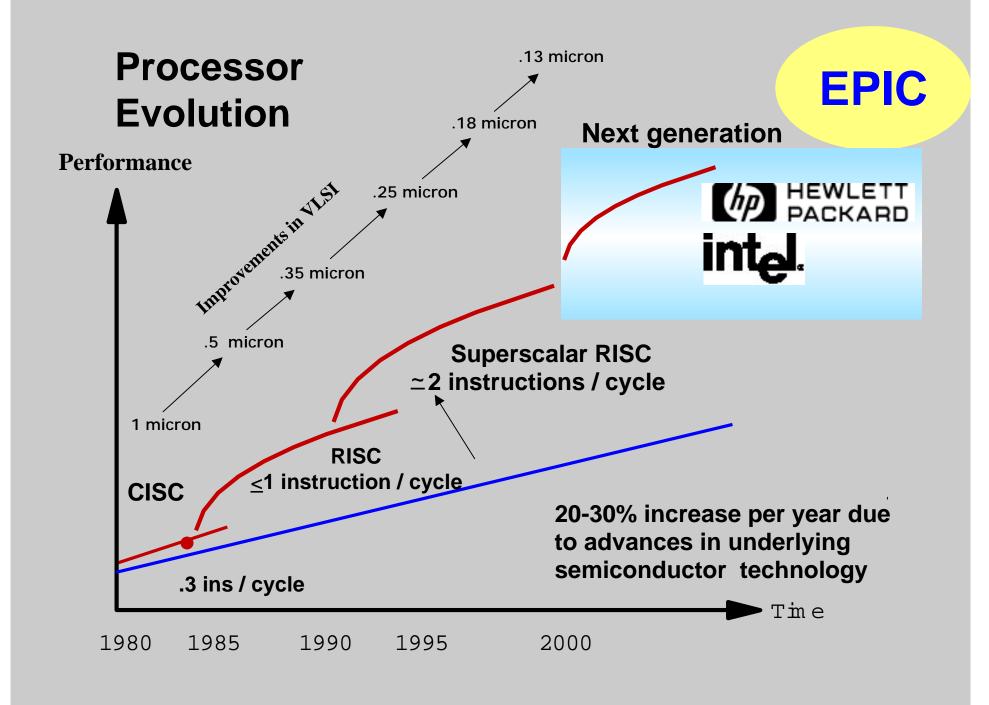

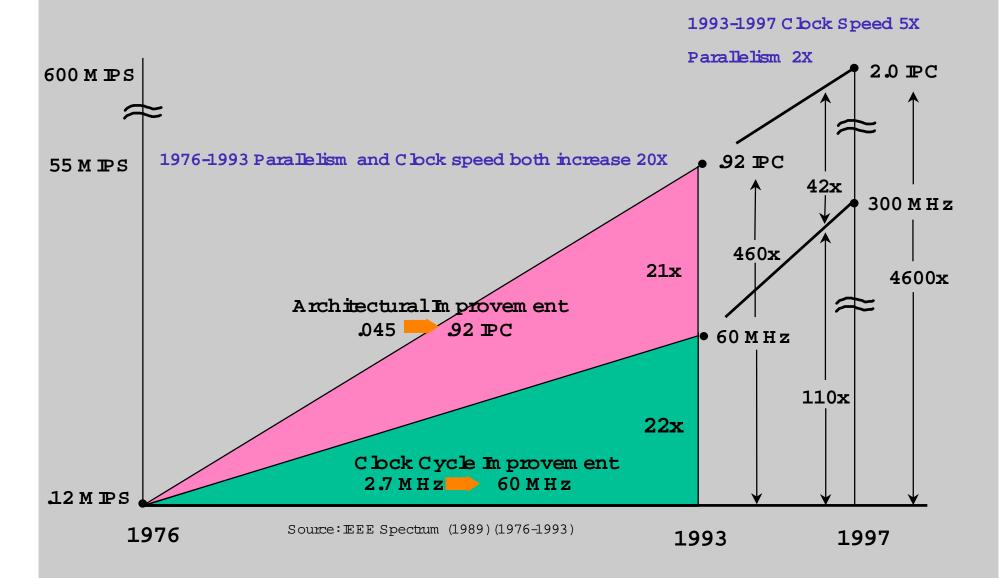

# M icroprocessor Perform ance G row th

# **Today's Architecture Challenges**

- Performance barriers :

- Memory latency

- Branches

- Loop pipelining and call / return overhead

- Headroom constraints :

- Hardware-based instruction scheduling

- Unable to efficiently schedule parallel execution

- Resource constrained

- Too few registers

- Unable to fully utilize multiple execution units

- Scalability limitations :

- Memory addressing efficiency

#### IA-64 addresses these limitations

### **IA-64 Mission**

- Overcome the limitations of today's architectures

- Provide world-class floating-point performance

- Support large memory needs with 64-bit addressing

- Protect existing investments

- Full binary compatibility with existing IA-32 instructions in hardware

- Full binary compatibility with PA-RISC instructions through software translation

- Support growing high-end application workloads

- E-business and internet applications

- Scientific analysis and 3D graphics

## Define the next generation computer architecture

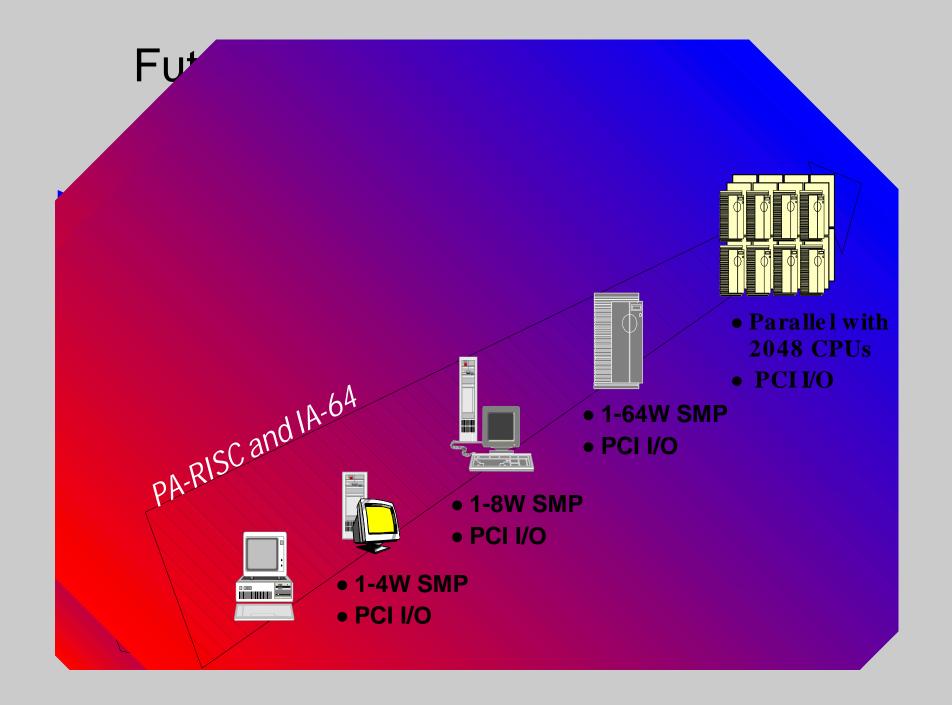

### Architecting a Smooth Transition to IA-64

#### Hardware

- Parallelpath of PA-RISC and IA-64

- IA -64-ready board upgradable system s

#### Operating system

- •HP-UX is IA-64 ready (m inorupdate)

- No adm in istrator/operator interface changes

- •Collaboration with Microsofton NT transition

- •HP Labs firstportofLinux to IA-64

- •S im ulators for early access to NT, Linux and HP-UX

#### Applications

- No forced application rewrites

- •No data m igration

- •No forced applications recompiles

- •PTAC for ISV Porting Certification

# PARISC will live on through IA-64

IA-64 retains many key PA-R ISC characteristics:

- 1-to-1 m apping of perform ance-sensitive m achine-level instructions

- PA-RISC virtualm em ory architecture

- Identical data form ats

- PA-RISC floating point (IA-64 is a superset)

- PA-RISC multimedia (IA-64 is a superset)

- PA-RISC graphics acceleration

- Many other features still kept confidential

Benefits for PARISC custom ers:

- Sm oother transition to IA-64 architecture designed in

- Easier ISV m igration means more applications available sooner

- Betterperform ance and reliability—functionality outsooner

Key:avoid 'dead ends" where vendor can 'tm ove custom ers forward

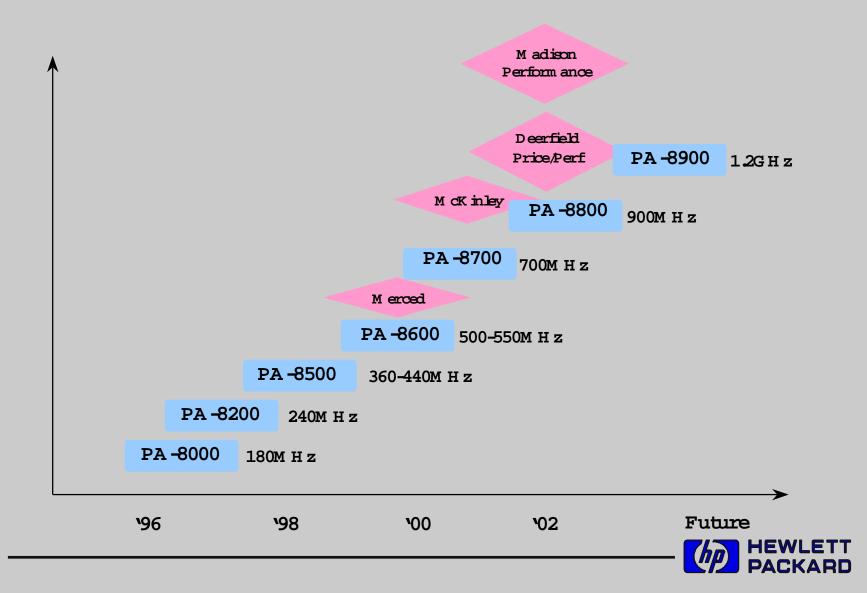

# **HP Microprocessor Roadmap**

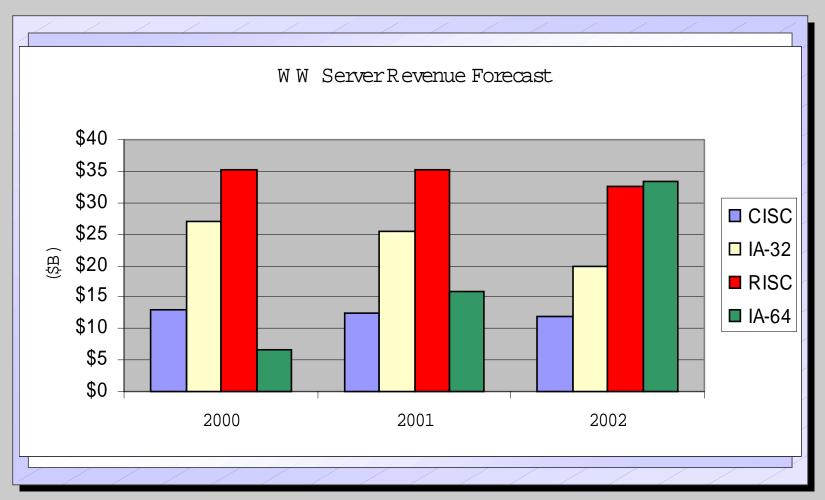

# DC Expects Rapid Rise of A-64

Source: DC 5/98: "Hew Lett-Packard Prepares for Rapid Rise of IA 64-Based Systems"

### Our Partners are Committed to IA-64

The software and Services you need when you need them!

Price Waterhouse

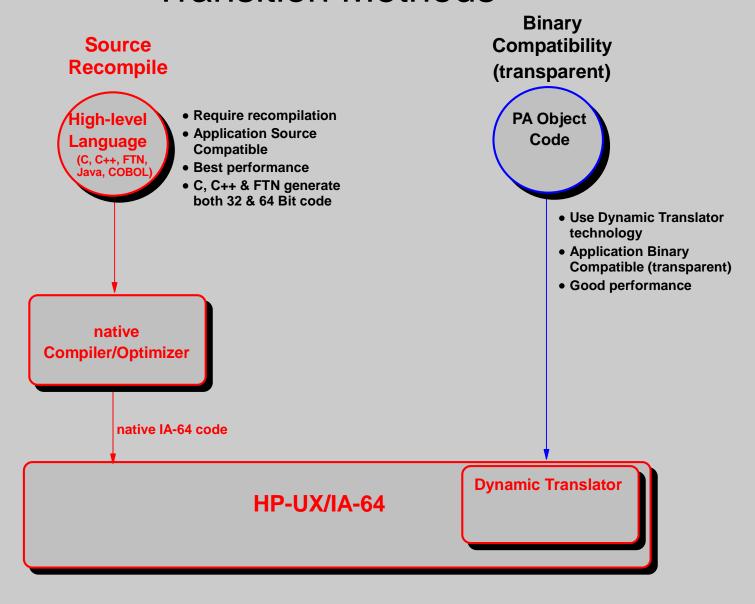

### **Transition Methods**

### **Source Code Impacts**

#### **Potential Source Impacts** When Moving to IA-64

A clear jumping-off point

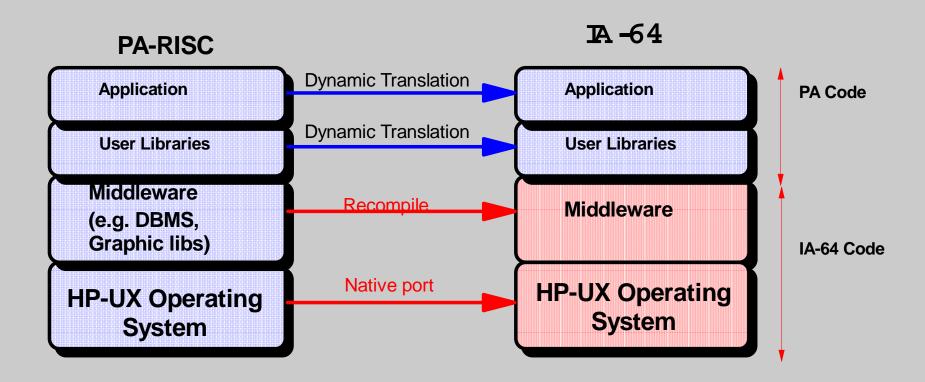

# **Execution Environment**

- A Mixed Environment

- Preserve the PA-RISC environment

- Allow incremental transition

# **Dynamic Translation**

- PA-RISC to IA-64 dynamic translator

- Features:

- Highly reliable

- Transparent

- Good performance

- Small set of limitations

- An integral part of HP-UX on IA-64, no installation required

- The Translator is user-level IA-64 code

- Invocation is automatic

- Optimization is unique to each execution

# **Full Binary Compatibility for PA-RISC**

### Transparency:

- Dynamic object code translator in HP-UX automatically converts PA-RISC code to native IA-64 code

- Translated code is cached for later reuse

#### Correctness:

- Has passed the same tests as the PA-8500

#### Performance:

- Close PA-RISC to IA-64 instruction mapping

- Translation on average takes 1-2% of the time Native instruction execution takes 98-99%

- Optimization done for wide instructions, predication, speculation, large register sets, etc.

- PA-RISC optimizations carry over to IA-64

## **Translator Limitations**

- If it doesn't run on the PA version of HP-UX 11.x, it won't run on IA-64 HP-UX 11.x

- No mixing of PA and IA-64 components

- PA executable w/ IA-64 shared libraries

- IA-64 executable with PA shared libraries

- vfork acts like fork

- No support for privileged instructions, which means:

- No kernel-intrusive codes

- No device drivers

- No home-grown operating systems

- No support for "/dev/kmem"

- No support for real-time or timing sensitive applications

- No support of signaling floating-point NaNs

- No support of ptrace and ttrace system calls

# Impact on system

- The Translator installs a translated code cache for each PA process running on the IA-64 system in the application's stack area.

- An additional 1-8MB of swap space, depending on the size of the process and the swap-space pressure on the system, will be needed by the translator for each PA process

- IA-64 systems will easily run many hundreds of PA processes simultaneously

### **Translated Mode - Performance**

- Databases, OS calls, IO will all be native code - Applications spending little of their time in user code will run with near Native mode performance

- Applications spending most of their time in the application code itself should be re-compiled

# And Remember, Intel says:

- Mckinley will double Merced's performance at introduction

- Mckinley will be available at clock speeds >1Ghz

### What to look out for

Understand your environm ent-Do you really know what code you run (Allofit) and where it cam e from ... ..

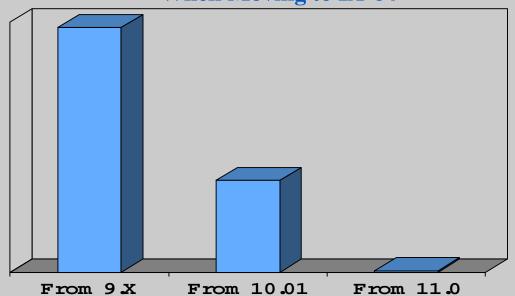

Are you on HP-UX 11 X - If not, Get there.

Are you dependent upon any code for which you do not have the source, and for which no A-64 version is likely to be available - and is that code perform ance sensitive?

There is no m ixed m ode.PA code cannot call A-64 code and vice-versa. Clientserver im plem entations can get around this.

# **Creating a Transition Plan**

- **\***Take inventory

- \*Ask your S/W vendors about their IA-64 plans

- \*Confirm that your sources are really current

- \*Take out the garbage

- \*If you are not there yet Plan a transition to 11.0

- **\***Use HP services if necessary for 9.X -> 10.X

- **\***Use the 11.X STK to scan 11.X issues

- **\***Understand your performance requirements

- **\*Set Native mode transition priorities**

- \*Can you keep running PA-RISC code (static apps?)

- \*Get help from HP or others if necessary

# Helping You Prepare for the Future

#### **Documentation**

HP-UX 9.x to 10.0 version B.10.01 Manual

9.X, 10.X, 11.X Release Notes

9.X to 10.X Transition Manual

11.0 Software Developers Guide

**IA-64 CDROM**

http://www.hp.com

http://software.hp.com/STK

http:/dtf.hp.com/dtf

http://www.hp.com/go/ia64

#### **Tools**

9.X ->10.X System Tools

9.X -> 10.X Application Tools

10.X -> 11.0 STK

11.0 -> 11.X (IA-64) STK

http://www.devresource.hp.com

#### **Services**

Response Center O.S. Upgrade Assistance Service

**EPIC Readiness Services**

**Developer Alliances Lab**

**Designing the Future Seminars**

**Customer Early Access Programs**

# What Do We Know About IA-64 and the HP 3000?

- New com parably perform ing PA →R ISC processors are being introduced through 2002/2003

- ▶ IA -64 M PE /iX will require a separate release

- User PA-R ISC applications will not have to be recompiled

- → CSY 's goal is to allow Classic HP 3000 binary code to run, unrecompiled on IA-64 HP 3000 Servers

- → Recom piled Classic and PA-RISC applications will run faster

- N ext generation servers will be board upgradeable to IA -64

- → M PE /iX support of IA -64 will occur beyond 2001

- When IA-64 M PE /iX is introduced, PA-R ISC M PE /iX will continue to be supported in parallel

Stay tuned form one details